首页:修订间差异

来自清华大学高性能处理器实验室

跳到导航跳到搜索

无编辑摘要 |

|||

| (未显示同一用户的81个中间版本) | |||

| 第2行: | 第2行: | ||

<!-- Author: Deyuan Guo --> | <!-- Author: Deyuan Guo --> | ||

<!-- Copyright ? 2009-2013 DSP Laboratory, Institute of Microelectronics, Tsinghua University. --> | <!-- Copyright ? 2009-2013 DSP Laboratory, Institute of Microelectronics, Tsinghua University. --> | ||

欢迎访问 | 欢迎访问 清华大学高性能处理器实验室! | ||

<!-- Two columns --> | <!-- Two columns --> | ||

| 第18行: | 第18行: | ||

本实验室隶属于清华大学微电子所,主要从事高性能处理器系统设计,类人智能研究。 | 本实验室隶属于清华大学微电子所,主要从事高性能处理器系统设计,类人智能研究。 | ||

实验室目前包括孙义和教授,[[何虎]]副教授,[[杨旭]]副教授,[[郭德源]] | 实验室目前包括孙义和教授,[[何虎]]副教授,[[杨旭]]副教授,[[郭德源]],陈晨,麻军平,王旭,李丽斯,李源,侯毓敏博士,赵烁。博士研究生龚汉文,李京洲,马鸣远,硕士研究生 刘旭东,陈怀郁,杨泽夏,于芳菲,朱菁菁,艾宁智,申高花。 | ||

* '''主要专注方向''' | * '''主要专注方向''' | ||

** 高性能数字信号处理器(DSP)设计 | ** 高性能数字信号处理器(DSP)设计 | ||

** 嵌入式高性能CPU IP设计 | ** 嵌入式高性能CPU IP设计 | ||

** 开源GPGPU | |||

** 计算存储一体计算机体系架构 | ** 计算存储一体计算机体系架构 | ||

** | ** 可解释因果学习算法 | ||

|- | |- | ||

| 第33行: | 第34行: | ||

=== ◇ 科研成果展示 === | === ◇ 科研成果展示 === | ||

|- | |||

| | |||

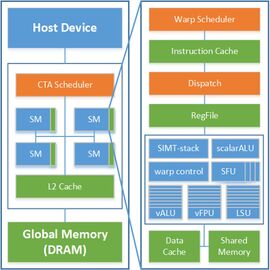

[[File:GPGPU.jpg|270px|thumb|乘影GPGPU架构]] | |||

** 乘影GPGPU是一款采用开源指令集RISC-V及其Vector扩展指令集设计的一款SIMT架构的GPGPU,也是世界首款基于RVV的GPGPU; | |||

** 目前已经开源发布。发布地址为:https://github.com/THU-DSP-LAB/, https://www.gitlink.org.cn/thu-dsp-lab | |||

** 开源代码包括乘影GPGPU源码,gcc工具链,OpenCL工具链和spike仿真器; | |||

** 与兆松科技合作开展乘影GPGPU OpenCL编译器开发; | |||

** 乘影GPGPU既保持了RISC-V Vector指令集的优势,又利用了SIMT架构扩展性好的特点,实现了开源指令集高性能GPGPU的设计。 | |||

** 开源网站:https://OpenGPGPU.org.cn | |||

[[File:Ventus_arch2.png|500px|Ventus microarch]] | |||

|- | |||

| | |||

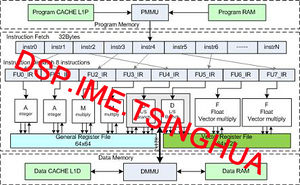

[[File:egret_pipeline.jpg|500px|thumb|Egret CPU流水线架构]] | |||

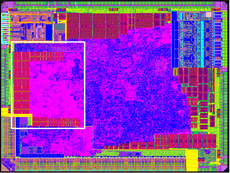

* '''兼容RISC-V指令集的Egret CPU'''[[File:thu-dsp-logo-60x44.bmp|20px]]''Egret CPU'' | |||

** 与厦门半导体投资集团有限公司合作,开发高性能RISC-V指令集嵌入式CPU。开发代号Egret。 | |||

** 支持RV32IMADCV指令集; | |||

** 支持内存管理及物理内存保护机制; | |||

** 支持定时器中断、软件中断以及最多64个外部中断; | |||

** I-Cache、D-Cache大小可配置,支持L1-Cache和L2-Cache; | |||

** 提供配套的嵌入式操作系统和软件工具链; | |||

** 指令并行度为2; | |||

** 单核性能不低于1.8 DMIPS/MHz, 2.88Coremark/MHz; | |||

** 采用SMIC 40nm LL工艺流片,频率不低于600MHz; | |||

** 采用UMC 28nm工艺流片的双核RISC-V SoC预计于2021年7月流片; | |||

** 与清华大学计算机系合作开发的RISC-V矢量扩展CPU于2020年12月流片,已经完成封装和测试。 | |||

[[File:Egret_layout.png|230px|Egret Layout]] [[File:Egret_chip.png|210px|Egret Chip]] | |||

[[File:Egret2_die.jpg|230px|Egret2 die Chip]] [[File:Egret2_chip.jpg|180px|Egret2 chip Chip]] [[File:Egret2_EVB.jpg|280px|Egret2 EVB Chip]] | |||

|- | |- | ||

| | | | ||

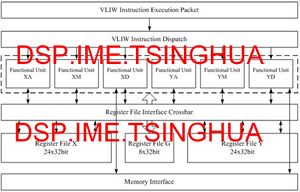

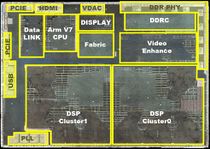

| 第41行: | 第70行: | ||

** 首次实现VLIW流水线分支预测功能 | ** 首次实现VLIW流水线分支预测功能 | ||

** 兼容ARM v7a 指令集,1.9DMIPS/MHz,实测频率150MHz(@SMIC130nm) | ** 兼容ARM v7a 指令集,1.9DMIPS/MHz,实测频率150MHz(@SMIC130nm) | ||

** 实现了模拟电路隐蔽型硬件木马和抗硬件木马设计 | ** 实现了模拟电路隐蔽型硬件木马和抗硬件木马设计 | ||

** 集成了嵌入式1Mb的ReRAM | ** 集成了嵌入式1Mb的ReRAM | ||

** | ** 成果发表在 Y. Hou, Hu He, etc., "On-Chip Analog Trojan Detection Framework for Microprocessor Trustworthiness," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 38, no. 10, pp. 1820-1830, Oct. 2019 | ||

[[File:Merlin.jpg|240px|Merlin Die]] [[File:Merlin_chip.jpg|180px|Merlin Chip]] | [[File:Merlin.jpg|240px|Merlin Die]] [[File:Merlin_chip.jpg|180px|Merlin Chip]] | ||

|- | |- | ||

| | | | ||

* '''仿生型自生长神经网''' | * '''仿生型自生长神经网''' | ||

** 依靠计算能力实现的人工神经网不具备强(通用)人工智能的能力 | ** 依靠计算能力实现的人工神经网不具备强(通用)人工智能的能力 | ||

| 第54行: | 第82行: | ||

** 生物神经网络具备后天生长特性,可以增加神经网络原来不具备的功能 | ** 生物神经网络具备后天生长特性,可以增加神经网络原来不具备的功能 | ||

** 生物神经网的记忆是分布式的,采用内容提取记忆的方式 | ** 生物神经网的记忆是分布式的,采用内容提取记忆的方式 | ||

** | ** 最新成果:Hu He, Qilin Wang, Xu Yang, Yunlin Lei, Jian Cai, Ning Deng, A memory neural system built based on spiking neural network, Neurocomputing (2021) (https://www.sciencedirect.com/science/article/pii/S0925231221002988); He Hu, Shang Yingjie, Yang Xu, Deng Ning, etc., Constructing an Associative Memory System Using Spiking Neural Network, Frontiers in Neuroscience,https://www.frontiersin.org/article/10.3389/fnins.2019.00650 ; He H, Yang X, Xu Z, Deng N, Shang Y, et al. (2019) Implementing artificial neural networks through bionic construction. PLOS ONE 14(2): e0212368. https://doi.org/10.1371/journal.pone.0212368; Xu Yang, Guo Liu, Songgaojun Deng, Zichao Wei, Hu He*, Yingjie Shang, Ning Deng. Artif Intell Rev (2018). https://doi.org/10.1007/s10462-018-9626-2 | ||

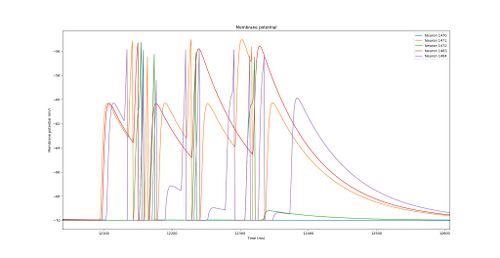

[[File:Neuronetwork.jpg|200px|Binoic Neural Network]] [[File:Spiking.jpg|500px|Spiking of memory]] | |||

|- | |- | ||

| | | | ||

| 第85行: | 第114行: | ||

** 论文:CDSP: A Solution for Privacy and Security of Multimedia Information Processing in Industrial Big Data and Internet of Things, https://doi.org/10.3390/s19030556 | ** 论文:CDSP: A Solution for Privacy and Security of Multimedia Information Processing in Industrial Big Data and Internet of Things, https://doi.org/10.3390/s19030556 | ||

[[File:Svac_chip.jpg|150px|SVAC SoC Chip]] [[File:Svac_layout.jpg|210px|SVAC SoC Die]] | [[File:Svac_chip.jpg|150px|SVAC SoC Chip]] [[File:Svac_layout.jpg|210px|SVAC SoC Die]] | ||

[[File:Reward.jpg|230px|Beijing Reward]] | |||

|- | |- | ||

| | | | ||

2024年3月20日 (三) 07:35的最新版本

欢迎访问 清华大学高性能处理器实验室!

|

|

Copyright © 2009-2019 DSP Laboratory, Institute of Microelectronics, Tsinghua University. All Rights Reserved. 清华大学微电子所数字信号处理器实验室 版权所有.