首页:修订间差异

来自清华大学高性能处理器实验室

跳到导航跳到搜索

无编辑摘要 |

无编辑摘要 |

||

| 第38行: | 第38行: | ||

:* 云计算处理器 | :* 云计算处理器 | ||

:* 密码处理器IP | :* 密码处理器IP | ||

|- | |||

|} | |||

{| class="wikitable" width="99%" style="border;1px" | |||

! style="text-align:left" | | |||

=== ◇ 科研成果展示 === | |||

|- | |||

| | |||

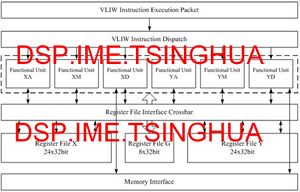

[[File:Lily.jpg|thumb|Lily处理器架构]] | |||

* '''可配置超长指令字处理器''' | |||

** 在2006年信息产业部集成电路发展资金的资助下,清华大学数字信号处理器实验室开始了商品化DSP的研究,开发代号LILY; | |||

** 体系结构相关论文“Architecture Design of A Variable Length Instruction Set VLIW DSP”已被清华学报英文版收录并发表; | |||

** 申请了两项体系结构专利(200810006836.7,200810101451.9)和三项指令专利(200910190205.2, 200910190203.3, 200910190204.8); | |||

** 该处理器拥有最高8路功能单元的VLIW内核设计,拥有两级缓存。其中一级数据缓存可以配置2路或者4路; | |||

** 完善的软件工具链,包括:基于Open64的C编译器,基于Binutils的二进制工具链,RTL级指令精度仿真器ISS; | |||

|- | |||

| | |||

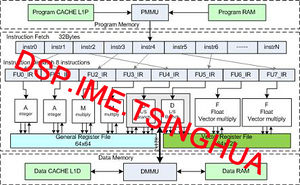

[[File:Magnolia.jpg|thumb|Magnolia处理器架构]] | |||

* '''VLIW架构通用处理器''' | |||

** 2009年设计完成的一款面向通用应用的的超长指令字处理器,开发代号Magnolia; | |||

** 该处理器利用VLIW架构提高指令并行度,并且设计了定点和浮点向量单元,提高数据并行度; | |||

** 32位指令宽度下,拥有近900条定点,浮点和向量指令; | |||

** 申请多项体系结构专利,并发表多篇论文; | |||

** 基于Open64的高性能C编译器,研究并提供编译器自动向量化支持; | |||

** 基于Gem5的模拟器支持程序级和操作系统级的周期精度模拟; | |||

** 基于Binutils的GNU标准二进制工具; | |||

|- | |||

| align="right" | [[科研成果 | 更多科研成果...]] | |||

|- | |- | ||

|} | |} | ||

2011年5月11日 (三) 05:04的版本

欢迎访问 清华大学微电子所 数字信号处理器实验室 (旧版入口)

|

|