|

|

| 第54行: |

第54行: |

| ** 这样既可以简化主控CPU的设计复杂度,降低功耗,又可以提高存储器访问效率; | | ** 这样既可以简化主控CPU的设计复杂度,降低功耗,又可以提高存储器访问效率; |

| ** 最终实现存储器计算架构; | | ** 最终实现存储器计算架构; |

| ** 目前该项目已经完成了基于gem5模拟的架构设计任务,提出了PIM编程范式,模拟器模拟结果符合预期。 | | ** 目前该项目已经完成了基于gem5模拟的架构设计任务,提出了PIM编程范式,模拟器模拟结果符合预期; |

| | ** 目前该项目进入FPGA实现阶段。 |

| |- | | |- |

| | | | | |

2016年9月30日 (五) 00:15的版本

欢迎访问 清华大学数字信号处理器课题组!

◇ 课题组简介

|

|

本课题组隶属于清华大学微电子所,主要从事高性能数字信号处理器系统设计研究。

课题组目前包括孙义和教授,何虎副教授,杨旭副教授,郭德源,麻军平,李正兴。 目前组内有博士研究生1名,硕士研究生7名。

- 主要专注方向

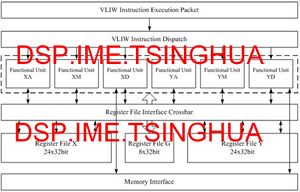

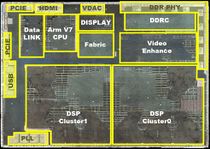

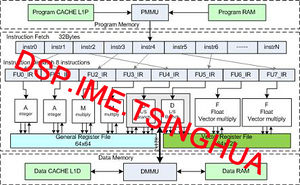

- 高性能数字信号处理器(DSP)设计

- 处理器指令精度模拟器研究

- 并行程序设计模型与编译技术

- 适应视频图像处理和科学计算的计算机体系结构

- 多核、众核片上系统

- 片上网络(NoC)设计

- 神经网络,类脑计算

|

◇ 专利列表

|

|

授权专利

- 一种超长指令字处理的方法和装置

- 一种超长指令字指令并行执行方法及装置

- 完成两次乘法两次加法两次位移的微处理器实现方法

- 微处理器(CN201010033646.1)

- 一种多周期指令执行方法和装置

- 支持同时多线程的超长指令字处理器结构

- 一种交替访问寄存器的装置及其方法

- 融合了顺序和VLIW的处理器体系结构及指令执行方法

受理专利

- 一种计算存储一体的分布式计算机架构

- 扩展处理器寄存器堆容量的方法

- 一种支持超标量与超长指令字混合架构处理器的分支预测方法

- 一种基于现场可编程门阵列实现神经网络计算的方法

- 一种以现场可编程门阵列的逻辑片为基本单元模拟生物神经元网络的方法

- 一种基于进化算法的自适应学习神经网络实现方法

- 一种自生成神经网络构建方法

|

|

|

Copyright © 2009-2016 DSP Laboratory, Institute of Microelectronics, Tsinghua University. All Rights Reserved. 清华大学微电子所数字信号处理器实验室 版权所有.