首页:修订间差异

来自清华大学高性能处理器实验室

跳到导航跳到搜索

无编辑摘要 |

无编辑摘要 |

||

| 第53行: | 第53行: | ||

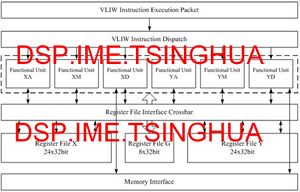

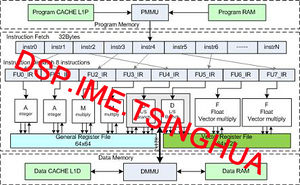

** 该处理器拥有最高8路功能单元的VLIW内核设计,拥有两级缓存; | ** 该处理器拥有最高8路功能单元的VLIW内核设计,拥有两级缓存; | ||

** 完善的软件工具链,包括:基于Open64的C编译器,基于Binutils的二进制工具链,RTL级指令精度仿真器ISS,基于gem5的软件模拟器; | ** 完善的软件工具链,包括:基于Open64的C编译器,基于Binutils的二进制工具链,RTL级指令精度仿真器ISS,基于gem5的软件模拟器; | ||

** 在LILY的基础上,研制出VLIW/RISC融合型通用处理器LILY2。该处理器吸收了VLIW显示并行,低功耗的优点,又同时具备通用RISC处理器编程友好的特点; | |||

** LILY2目前完成了RTL和GCC编译器,gem5模拟器等设计工作。 | |||

|- | |- | ||

| | | | ||

2013年10月12日 (六) 06:48的版本

欢迎访问 清华大学数字信号处理器实验室!

|

|

Copyright © 2009-2013 DSP Laboratory, Institute of Microelectronics, Tsinghua University. All Rights Reserved. 清华大学微电子所数字信号处理器实验室 版权所有.